# Single-Crystalline Silicon-Based Heterojunction Photodiode Arrays on Flexible Plastic Substrates

Sangwook Lee, Juree Hong, Ja Hoon Koo, Seulah Lee, Kwanghyun Lee, Seongil Im, and Taeyoon Lee

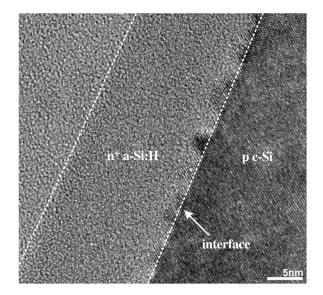

Abstract-A silicon-based photodiode array was fabricated on a flexible polyethylene terephthalate substrate using a transfer printing technique. A heterojunction structure composed of a 15-nm-thick highly doped hydrogenated amorphous-silicon (n<sup>+</sup> a-Si:H) layer and a 3- $\mu$ m-thick p-type single-crystal silicon (p c-Si) membrane layer was adopted as the active layer of the flexible photodiode. The highly ordered photodiode array formed on the flexible substrate exhibited superior stability in electrical properties under bent conditions with no mechanical deformation. The variation of the spectral quantum efficiency (QE) under short--wavelength light illumination ( $\lambda \leq 580$  nm) was in excellent agreement with that of a heterojunction photodiode composed of a-Si:H and a bulk c-Si substrate. Relatively low QE values were observed under longer wavelength ( $\lambda > 600$  nm) illumination due to the finite thickness of the active layer. The C-V measurement results of the fabricated photodiode array were in accordance with the abrupt junction model. A closer inspection of the junction area of the device using high-resolution cross-sectional transmission micrograph exhibited an interface depth of  $2 \pm 0.5$  nm, which is unavoidable in plasma-enhanced a-Si:H deposition processes.

*Index Terms*—Flexible device, heterojunction, silicon-based photodiode, transfer printing.

## I. INTRODUCTION

**F** LEXIBLE or bendable electronic devices fabricated on plastic substrates have received significant attention as candidates for use in photodetectors, solar cells, displays, and transistors due to their light weight, low manufacturing cost, and folding capability at uneven surfaces in diverse applications [1]–[5]. Polymer or organic materials have been used widely as active layers in these devices since they are compatible with plastic substrates that can endure rather low thermal budgets in their fabrication processes [6], [7]. However, organic-based flexible devices have a certain limitation in the optical performance; in the case of organic semiconductors (e.g., poly(3-hexylthiophene) and poly[2-

Manuscript received March 5, 2011; revised May 25, 2011 and July 5, 2011; accepted July 7, 2011. Date of publication August 22, 2011; date of current version September 21, 2011. This work was supported in part by the National Research Foundation of Korea under Grant 2010-50193, by the KARI–University Partnership Program, and by the Priority Research Centers Program of National Research Foundation of Korea of the Ministry of Education, Science and Technology under Grant 2009-0093823. The review of this paper was arranged by Editor A. G. Aberle.

S. Lee, J. Hong, J. H. Koo, S. Lee, and T.-Y. Lee are with Nanobio Device Laboratory, School of Electrical and Electronic Engineering, Yonsei University, Seoul 120-749, Korea (e-mail: taeyoon.lee@yonsei.ac.kr).

K. Lee and S. Im are with Electron Device Laboratory, Department of Physics, Yonsei University, Seoul 120-749, Korea.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2011.2162241

methoxy-5-(2'-ethylhexoxy)-1,4-phenylenevinylene]), its light absorption and quantum efficiency (QE) in the range of visible light (380-750 nm) are much smaller than those of inorganic semiconductors due to its large band gap (> 2 eV) [8], [9]. To circumvent these restrictions and realize high-performance flexible electronics, printing techniques that allow the relocation of inorganic single-crystalline-silicon (c-Si) thin membranes on flexible substrates have been researched extensively [10]–[12]. In c-Si devices, adequate thickness of the active layer in the range of few tens of micrometers is required to obtain sufficient absorption of ambient light for high photon-conversion efficiency. However, this thickness requirement for the rigid inorganic active layer conflicts with its ability to sustain mechanical stability under bending conditions [13]. Thus, to obtain a flexible device, the absorption ability has to be sacrificed somewhat in exchange with the thickness of the active layer.

In a c-Si based photodiode, heterojunction structure with a hydrogenated amorphous-silicon (a-Si:H) layer has been receiving great attention due to its highly efficient, simple, and cost-effective fabrication process [14]–[16]. The related research has been focused on the carrier transport mechanisms and the electrical characteristics of a-Si:H/c-Si structure in various applications including solar cells, photodetectors, and bipolar transistors [17]–[19]. However, none has yet reported on the fabrication of a flexible photodiode based on this a-Si:H/c-Si heterojunction system.

In this paper, the challenge of making the active layer thinner to the extent of being durable in a bended state was addressed using an a-Si:H/c-Si heterojunction photoarray printed on a flexible polyethylene terephthalate substrate. The 3- $\mu$ m-thick active layer was detached from the top of a silicon-on-insulator (SOI) wafer by a hydrofluoric acid (HF) wet-etching process and transferred onto a plastic substrate using an elastomeric polydimethylsiloxane (PDMS) stamp. The relocated array of cells was highly ordered with no mechanical deformation. The device characteristics were extracted from the I-V and C-V measurements. High-resolution cross-sectional transmission electron microscopy (HR-XTEM) was utilized to investigate the interface of the a-Si:H/c-Si heterojunction. The photodiode array assembled on the plastic substrate exhibited durable flexibility with excellent electrical performance.

### **II. EXPERIMENTAL PROCEDURES**

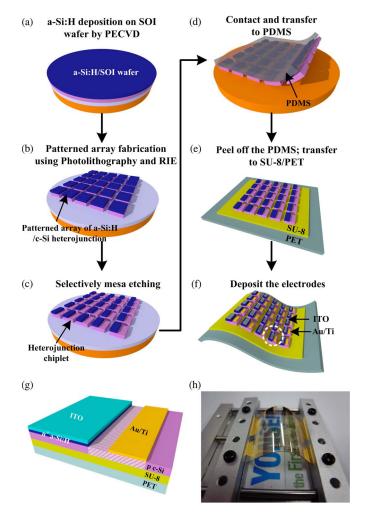

Fig. 1(a)–(f) illustrates schematically the procedures used to obtain the a-Si:H/c-Si heterostructure thin-film photodiode array on a plastic substrate. First, the polished SOI wafers with a  $3-\mu$ m-thick top layer of p-type silicon and a buried oxide of

Fig. 1. (a)–(f) Schematic illustration of the process used to fabricate the heterojunction photoarray on a flexible substrate. (g) Perspective schematic of the fabricated a-Si:H/c-Si photodiode chiplet. (h) Photograph of the fabricated photo array on a bent flexible PET substrate.

200 nm were prepared. They were cleaned at 70 °C for 10 min in an RCA solution (1:1:5(v/v/v) NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O), followed by dipping in a buffered-oxide-enchant solution for 30 s to remove the native oxide. To obtain heterojunction active layers, the 15-nm-thick highly doped n-type  $(n^+)$  a-Si:H thin films were deposited on the SOI wafers using a plasma-enhanced chemical vapor deposition (PECVD) system in a gas mixture of  $SiH_4$  (20 sccm) and  $PH_3$  (1% diluted in 99%  $H_2$  with 10 sccm) at the setpoint temperature of 350 °C [see Fig. 1(a)]. The patterned arrays of a-Si:H/c-Si heterojunction structure were fabricated via photolithography combined with reactive ion etching (RIE) using  $SF_6$  and  $O_2$  mixture [see Fig. 1(b)]. Then, the a-Si:H layer was mesa-etched selectively with the dimensions of 200  $\mu$ m (width) × 250  $\mu$ m (length) to expose the p-type (p) c-Si for the individual front-side contact, as shown in Fig. 1(c). To separate the heterojunction active layer from the mother wafer, the samples were immersed in aqueous HF with a concentration of 49%-51% to etch the buried oxide. After the etching process was carried out, the photodiode chiplets in the array form were settled down with maintaining their initial positions on the mother substrate via Van der Waals' force. Prior to transferring the fully detached chiplet array, the PDMS was cured for 24 h at room temperature using a mixture consisting of a Sylgard 184 base and a curing agent at a volume composition ratio of 10:1 [20]. The PDMS stamp was brought into contact with the top surface of the detached arrays, and they were peeled off completely from the mother wafer [see Fig. 1(d)]. Separately, the PET films were cleaned successively with acetone, isopropanol, and deionized water. The surfaces of the PET substrates were treated with O<sub>2</sub> plasma at 300 W for 30 s and were spin-coated with an adhesive SU-8 2002 layer. The SU-8/PET sample was prebaked at 95 °C for 5 min; then, the transferred arrays on the PDMS were attached onto the prepared SU-8/PET substrate at 95 °C for 5 min [see Fig. 1(e)]. Then, the photodiode array/SU-8/PET samples were baked at 115 °C for 10 min to ensure cross-linking of the SU-8 bonding material. To fabricate the front-side transparent electrode (n<sup>+</sup> a-Si:H contact), a 100-nm-thick indium-tin-oxide (ITO) layer with a dimension of 150  $\mu$ m  $\times$  200  $\mu$ m was deposited selectively with a shadow mask on the  $n^+$  a-Si:H layer using a direct-current magnetron-sputter deposition system with SnO<sub>2</sub> (90%) and  $In_2O_3$  (10%) targets. Finally, the 50-nm-thick Au electrode (200  $\mu$ m × 100  $\mu$ m) was evaporated thermally on the exposed p c-Si layer [see Fig. 1(f)]. Fig. 1(g) exhibits the perspective view of a single cell with both the ITO and Au/Ti electrodes on the top side (a lateral structure) denoted with the white circle in Fig. 1(f). The lateral structure was adopted in this experiment due to the difficulties in the formation of the backside electrodes of the proposed flexible photodiodes. Fig. 1(h) shows an image of the fabricated photodiode array on a bent PET substrate.

The I-V characteristics measurements were performed using a HP4145B semiconductor parameter analyzer. The spectral photoresponsivity was characterized using a light source (Oriel Optical System, 500 W Hg-arc lamp) with a monochromator covering the range of 400 to 900 nm. C-V characteristics were measured under dark conditions at 1 MHz using a KEITHLEY 590 C-V analyzer. The interface of the a-Si:H/c-Si heterojunction active layer was investigated using TEM (FEI Tecnai F20).

#### **III. RESULTS AND DISCUSSION**

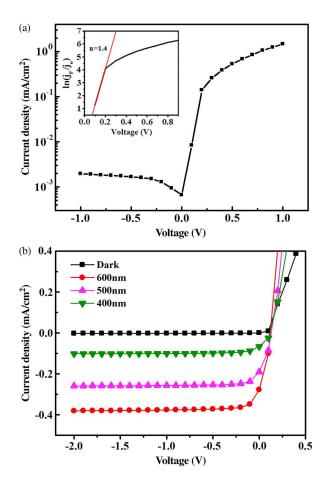

Fig. 2(a) shows the representative semilogarithmic I-V curve of n<sup>+</sup> a-Si:H/p c-Si heterojunction photoarray on a flexible PET substrate without illumination, revealing that the fabricated diode exhibits a good rectifying behavior. The inset in Fig. 2(a) shows  $\ln(j_F/j_0)$  as a function of forward-bias voltage, where  $j_F$  is the forward-current density and  $j_0$  is the saturation current density. From the inset graph, the diode ideality factor n of the fabricated device was obtained using the following diode equation [8]:

$$j_F = j_0 \left\{ \exp\left[\frac{q(V - j_F R_S)}{nkT}\right] - 1 \right\}$$

(1)

where q is the electron charge, V is the applied voltage,  $R_s$  is the series resistance of the diode structure, k is the Boltzmann's constant, and T is the absolute temperature. The calculated n in the low-level injection region was 1.44. The deviation of n from unity may be attributed to the recombination of

Fig. 2. (a) Semilogarithmic I-V characteristics of a-Si:H/c-Si heterostructure under the dark condition. The inset shows  $\ln(j_F/j_0)$  as a function of forward bias at the low-bias regime. (b) I-V characteristics of the a-Si:H/c-Si flexible photodiode array as a function of the illumination wavelength. The incident optical power was normalized at 1 mW.

electrons and holes in the space-charge region.  $R_s$  was also obtained in the high-forward-bias region using (1), which was a considerably high value of  $\approx 400 \text{ k}\Omega$ . The  $R_s$  of the fabricated device is composed of the contact resistance between the ITO and  $n^+$  a-Si:H, the resistance of the  $n^+$  a-Si:H layer, the resistance of the depletion region, the resistance of the bulk p c-Si layer, and the contact resistance between p c-Si and Au/Ti electrode. It can be expected that the high value of  $R_s$  was originated from an additional resistive part with dimensions of  $200 \ \mu m \times 170 \ \mu m \times 3 \ \mu m$  (width  $\times$  length  $\times$  height) resulting from the use of a lateral structure, i.e., indicated as a shaded region in Fig. 1(g), which was estimated to be approximately 45 k $\Omega$ . In addition, the poor contact between the p c-Si and the Au electrode could also contribute to this large  $R_s$ ; their interface could be damaged during the RIE process to expose the front-side contact area, which may cause a high contact resistance, and the adequate postannealing treatment after the contact formation in the fabricated device was limited due to the low thermal budget of the PET substrate.

Fig. 2(b) shows the I-V characteristics of the n<sup>+</sup> a-Si:H/ p c-Si heterojunction photoarray on a flexible PET substrate under illumination with different wavelengths  $\lambda$ . The photodiodes were biased up to -2 V under dark and illumination conditions with wavelengths of 400, 500, and 600 at room

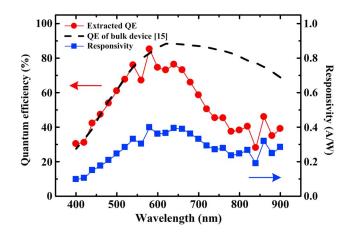

Fig. 3. Extracted spectral QE and corresponding responsivity as functions of the wavelength of the incident photons. For comparative analysis, the dashed line represents the data set in [15], showing the QE of a 10-nm-thick a-Si:H/bulk c-Si device.

temperature. The incoming power of the light illumination with various wavelengths was normalized at 1 mW, and the lights were projected at the front side of the fabricated photodiode arrays. Regardless of the incident wavelength, all of the reverse currents under illumination increased proportionally as a function of  $V^{1/2}$  in the low bias region from 0 to -0.5 V and were nearly saturated afterward. The photocurrents under different illumination of  $\lambda$  at the -2 V condition were 0.1 mA/cm<sup>2</sup> at 400 nm, 0.26 mA/cm<sup>2</sup> at 500 nm, and 0.38 mA/cm<sup>2</sup> at 600 nm. Such variation in the photocurrents with varying illumination of  $\lambda$  could be attributed to the fact that the photon flux changes with  $\lambda$  even when the illumination intensity was normalized. As shown in Fig. 2(b), the I-V characteristics under the different light illuminations are not the shifted replicas of the dark I-Vcurve, which might be originated from the changes in the  $R_s$ . Due to the additional resistive part in the proposed lateral structure, the fabricated device performance is more dependent on the variations of  $R_s$  compared with that of the vertically structured devices. The values of  $R_s$  are closely related to the amount of carrier concentration, which could be affected by the amount of light absorption in the fabricated device [21]. In our case, the light absorption is maximized when illuminated by light with  $\lambda$  of 600 nm (will be discussed in detail later, shown Fig. 3) and accordingly, the value of  $R_s$  is minimized, leading to a dramatic increase in the curvature of the I-V curve at the forward-bias region. The current in the dark remained almost constant with increasing reverse bias voltage, indicating that the flexible photodiode is well fabricated without any degradation even throughout the transfer printing process.

Fig. 3 shows the QE and the corresponding photoresponsivity of the transferred photoarrays as the functions of  $\lambda$  of the illumination source, which ranges from 400 to 900 nm. The extracted QE increased nearly linearly from 30% for  $\lambda =$ 400 nm to 85% for  $\lambda = 580$  nm before decreasing to 39% for  $\lambda = 900$  nm. A similar tendency can be found in the spectral photoresponsivity as the QE, as expected. The dependence of QE on the wavelength in the short-wavelength regime ( $\lambda \leq$ 580 nm) can be related to the probability of recombination of generated electron-hole (e–h) pairs. Due to the high absorption

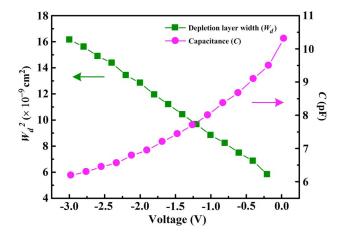

Fig. 4. Square of the depletion layer width  $W_d^2$  and capacitance C as the functions of the applied voltage V at 1 MHz.

coefficient of silicon for short-wavelength incident photons, most of the photons are absorbed near the surface, resulting in the generation of e-h pairs. However, since the top layer of our fabricated structure is an a-Si:H film, the defect density can be expected to be very high; thus, a considerable amount of the generated e-h pairs are subject to recombination, leading to a low QE value. In addition, the use of a polished SOI wafer in the heterojunction structure, resulting in the reflection loss, could contribute partially to this low QE. The highest QE of the transferred photoarrays was achieved at  $\lambda = 580$  nm. This can be ascribed to the fact that the thickness of the active layer of the fabricated photoarray was 3  $\mu$ m. For a comparative analysis, the appropriate data set from the work of Borchert et al. [15], who investigated the spectral QE of a heterojunction photonic device in a c-Si bulk wafer while varying the thickness of the a-Si:H layer, was retrieved. The dashed line in Fig. 3 indicates the QE obtained from their 10-nm-thick a-Si:H/bulk c-Si heterojunction in [15], which is well consistent with our experimental results in the shortwavelength region. The estimated penetration depth of the monochromatic light with  $\lambda = 600$  nm in the c-Si is approximately 3  $\mu$ m [21], which is consistent with the thickness of the active layer of our photoarray. Thus, at wavelengths below 600 nm, the electrical characteristics of our fabricated thin-film photoarray are similar to those of a bulk silicon device. However, with illumination with longer wavelengths ( $\lambda \ge 600$  nm), the QE of the photoarray was lower than that of the bulk silicon device. Such differences in the QE can be attributed to the fact that the thickness of our active layer was smaller than the penetration depth of longer wavelength light ( $\lambda \geq$ 600 nm) in silicon. Thus, a substantial amount of the longwavelength incident light penetrated through the silicon film of the photodiode array, causing less e-h generation, which in turn led to a considerable decrease in the QE and photoresponsivity.

Fig. 4 exhibits the variations of the square of the depletion layer width  $W_d^2$  and the capacitance of the fabricated flexible photodiode array when varying the applied voltage from -3 to 0 V. The C-V measurements were carried out at 1 MHz. This frequency is high enough to neglect the dielectric relaxation process in a-Si:H [22]. Thus, the total capacitance of the device can be regarded as the series capacitance of the a-Si:H layer

Fig. 5. HR-XTEM micrograph of the a-Si:H/c-Si interface.

and the c-Si layer. The capacitance of the a-Si:H layer may be a constant value, and the capacitance of c-Si depends on the depletion width of the junction, which varies with the applied voltage. Assuming that this junction follows the abrupt heterojunction model, we can express the dependence of  $W_d$  on the applied voltage as follows [23]:

$$W_d^2 = \left(\frac{\varepsilon_0 \cdot \varepsilon_s}{C} - L\right)^2 = \frac{2\varepsilon_0 \varepsilon_s N_I}{q N_A (N_I + N_A)} (V_D - V) \quad (2)$$

where L is the thickness of the a-Si:H layer,  $\varepsilon_0$  is the free-space permittivity,  $\varepsilon_s$  is the dielectric constant of a-Si:H and c-Si, q is the electronic charge, C is the capacitance of the depletion layer,  $N_I$  is the effective density of the donor-like states in a-Si:H,  $N_A$  is the doping concentration of c-Si, and  $V_D$  is the diffusion voltage. In particular, in the case of our fabricated n<sup>+</sup> a-Si:H/p c-Si heterojunction, the carrier density and effective donor-like states of the n<sup>+</sup>-layer are much higher than that of the p-layer. Hence, (2) can be simplified as follows [24]:

$$W_d^2 = \frac{2\varepsilon_0\varepsilon_s}{qN_A}(V_D - V).$$

(3)

As shown in (3), the magnitude of  $N_A$  can be deduced graphically from the slope of the  $W_d^2$  versus V curve. The estimated  $N_A$  value obtained from the slope of the plot in Fig. 4 is  $3.43 \times 10^{15}$  cm<sup>-3</sup>, which is almost identical to the doping concentration of p c-Si in this paper  $(2.3 \pm 1.1 \times 10^{15} \text{ cm}^{-3})$ . As shown in Fig. 4,  $W_d^2$  has a linear relationship with the applied voltage, indicating that the abrupt heterojunction model is applicable to our fabricated system [22]. Consequently, it was confirmed that the fabricated junction was electrically abrupt.

Fig. 5 represents a typical HR-XTEM image of the a-Si:H/ c-Si heterojunction interface of the fabricated photoarray showing a slightly rugged interface. Such an uneven interface can be caused generally by either the amorphization of the c-Si by plasma damage or the epitaxial growth of the c-Si into the a-Si:H matrix during the PECVD process of the thin a-Si:H layer [25]–[27]. In our case, the faintly rugged interface may have been formed due to the epitaxial growth of c-Si, which was facilitated by the PECVD process with sufficiently high deposition temperature for the epitaxial growth of c-Si. This irregular interface played a substantial role in the degradation of the electrical properties of the fabricated devices in earlier reports [28], [29] as the interface contained much structural defects. In contrast, it seems that the amount of local defects originated from the interface in our photoarrays was comparatively small, and thus their effect on the electrical properties could have been minor. As shown in Fig. 5, the thickness of the epitaxial grown c-Si layer in the interface area was approximately  $2 \pm 0.5$  nm, which was relatively small compared with those of the previously reported structures [25], [27], inferring that the electrical degradation of our fabricated photodiode by interfacial defect states might also be comparably small. Thus, combining these results, we conclude that the heterojunction photoarray was well fabricated with minimal degradation of the electrical properties by the deformed heterojunction interface.

#### **IV. CONCLUSION**

The device performances of a transfer-printed a-Si:H/c-Si heterojunction photoarray on a PET substrate were investigated using I-V and C-V measurements and responsivity tests under illumination at different wavelengths. The transferred photoarray chiplets were highly ordered and did not show any mechanical deformation after repeated folding–unfolding operation. The fabricated photodiode exhibited a low level of dark current and high photosensitivity. The decreased photoresponsivity with illumination with a long wavelength can be related to the light penetration depth, which exceeds the thickness of the active layer. By combining the HR-XTEM analysis and C-V measurement results, we demonstrated that the fabricated heterojunction active layer was electrically abrupt with an interface with small roughness, which was applicable in various flexible electronic applications.

#### REFERENCES

- R. Paetzold, K. Heuser, D. Henseler, S. Roeger, G. Wittmann, and A. Winnacker, "Performance of flexible polymeric light-emitting diodes under bending conditions," *Appl. Phys. Lett.*, vol. 82, no. 19, pp. 3342– 3344, May 2003.

- [2] A. B. Chwang, M. A. Rothman, S. Y. Mao, R. H. Hewitt, M. S. Weaver, J. A. Silvernail, K. Rajan, M. Hack, J. J. Brown, X. Chu, L. Moro, T. Krajewski, and N. Rutherford, "Thin film encapsulated flexible organic electroluminescent displays," *Appl. Phys. Lett.*, vol. 83, no. 3, pp. 413– 415, Jul. 2003.

- [3] Y. Ichikawa, T. Yoshida, T. Hama, H. Sakai, and K. Harashima, "Production technology for amorphous silicon-based flexible solar cells," *Solar Energy Mater. Solar Cells*, vol. 66, no. 1–4, pp. 107–115, Feb. 2001.

- [4] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and M. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, pp. 488–492, Nov. 2004.

- [5] M. A. Meitl, Y. Zhou, A. Gaur, S. Jeon, M. L. Usrey, M. S. Strano, and J. A. Rogers, "Solution casting and transfer printing single-walled carbon nanotube films," *Nano Lett.*, vol. 4, no. 9, pp. 1643–1647, 2004.

- [6] R. Hamers, "Flexible electronic futures," *Nature*, vol. 412, no. 6846, pp. 489–490, Aug. 2001.

- [7] S. R. Forrest, "The path to ubiquitous and low-cost organic electronic appliances on plastic," *Nature*, vol. 428, no. 6986, pp. 911–918, Apr. 2004.

- [8] T. F. Schulze, L. Korte, E. Conrad, M. Schmidt, and B. Rech, "Electrical transport mechanisms in a-Si: H/c-Si heterojunction solar cells," *J. Appl. Phys.*, vol. 107, no. 2, pp. 023711-1–023711-13, Jan. 2010.

- [9] M. Tsai and H. Meng, "Electron traps in organic light-emitting diodes," J. Appl. Phys., vol. 97, no. 11, pp. 114 502-1–114 502-7, Jun. 2005.

- [10] H. Jiang, D.-Y. Khang, J. Song, Y. Sun, Y. Huang, and J. A. Rogers, "Finite deformation mechanics in buckled thin films on compliant supports," *Proc. Nat. Acad. Sci.*, vol. 104, no. 40, pp. 15607–15612, 2007.

- [11] J. Song, H. Jiang, Y. Huang, and J. A. Rogers, "Mechanics of stretchable inorganic electronic materials," J. Vac. Sci. Technol. A, Vac. Surf. Films, vol. 27, no. 5, pp. 1107–1125, 2009.

- [12] M. Meitl, Z.-T. Zhu, V. Kumar, K. Jae, X. Feng, Y. Y. Huang, I. Adesida, R. G. Nuzzo, and J. A. Rogers, "Transfer printing by kinetic control of adhesion to an elastomeric stamp," *Nature Mater.*, vol. 5, no. 1, pp. 33– 38, 2006.

- [13] M. B. Schubert and J. H. Werner, "Flexible solar cells for clothing," *Mater. Today*, vol. 9, no. 6, pp. 42–50, Jun. 2006.

- [14] M. F. Baroughi, R. Jeyakumar, Y. Vygranenko, F. Khalvati, and S. Sivoththaman, "Fabrication and characterization of amorphous Si/crystalline Si heterojunction devices for photovoltaic applications," *J. Vac. Sci. Technol. A, Vac. Surf. Films*, vol. 22, no. 3, pp. 1015–1019, May 2004.

- [15] D. Borchert, G. Grabosch, and W. R. Fahrner, "Preparation of (n) a-Si: H/(p) c-Si heterojunction solar cells," *Solar Energy Mater. Solar Cells*, vol. 49, no. 1–4, pp. 53–59, Dec. 1997.

- [16] F. Roca, G. Sinno, G. Di Francia, P. Prosini, G. Fameli, P. Grillo, A. Citarella, F. Pascarella, and D. della Sala, "Process development of amorphous silicon/crystalline silicon solar cells," *Solar Energy Mater. Solar Cells*, vol. 48, no. 1–4, pp. 15–24, Nov. 1997.

- [17] B. Jagannathan, W. A. Anderson, and J. Coleman, "Amorphous silicon/ p-type crystalline silicon heterojunction solar cells," *Solar Energy Mater. Solar Cells*, vol. 46, no. 4, pp. 289–310, Jul. 1997.

- [18] J. Symons, J. Nijs, and R. P. Mertens, "The emitter-base interface current in silicon bipolar transistors with emitters deposited by plasma-enhanced CVD," *IEEE Trans. Electron Devices*, vol. 36, no. 12, pp. 2889–2894, Dec. 1989.

- [19] L. Ping, Y. Q. Li, and C. A. T. Salama, "A heterojunction bipolar transistor with a thin α-Si emitter," *IEEE Trans. Electron Devices*, vol. 41, no. 6, pp. 932–935, Jun. 1994.

- [20] E. A. Wilder, S. Guo, S. Lin-Gibson, M. J. Fasolka, and C. M. Stafford, "Measuring the modulus of soft polymer networks via a bucklingbased metrology," *Macromolecules*, vol. 39, no. 12, pp. 4138–4143, 2006.

- [21] S. O. Kasap, Principles of Electronic Materials and Devices. New York: McGraw-Hill Int. ed., 2006.

- [22] S. Sze and K. Ng, *Physics of Semiconductor Devices*. Hoboken, NJ: Wiley-Blackwell, 2007.

- [23] H. Matsuura, T. Okuno, H. Okushi, and K. Tanaka, "Electrical properties of n amorphous/p crystalline silicon heterojunctions," J. Appl. Phys., vol. 55, no. 4, pp. 1012–1019, Feb. 1984.

- [24] Y. J. Song, M. R. Park, E. Guliants, and W. A. Anderson, "Influence of defects and band offsets on carrier transport mechanisms in amorphous silicon/crystalline silicon heterojunction solar cells," *Solar Energy Mater. Solar Cells*, vol. 64, no. 3, pp. 225–240, Oct. 2000.

- [25] T. H. Wang, E. Iwaniczko, M. R. Page, D. H. Levi, Y. Yan, H. M. Branz, and Q. Wang, "Effect of emitter deposition temperature on surface passivation in hot-wire chemical vapor deposited silicon heterojunction solar cells," *Thin Solid Films*, vol. 501, no. 1/2, pp. 284–287, Apr. 2006.

- [26] I. Sakata, M. Yamanaka, and R. Shimokawa, "Back-surface-field effects at the heterojunctions between boron-doped p-type hydrogenated amorphous silicon and crystalline silicon in thin-film crystalline silicon solar cells," *Jpn. J. Appl. Phys. 1, Regul. Pap. Short Notes Rev. Pap.*, vol. 44, pp. 7332–7339, 2005.

- [27] S. De Wolf and M. Kondo, "Abruptness of a-Si:H/c-Si interface revealed by carrier lifetime measurements," *Appl. Phys. Lett.*, vol. 90, no. 4, pp. 042111-1–042111-3, 2007.

- [28] T. H. Wang, E. Iwaniczko, M. R. Page, D. H. Levi, Y. Yan, V. Yelundur, H. M. Branz, A. Rohatgi, and Q. Wang, "Effective interfaces in silicon heterojunction solar cells," in *Conf. Rec. 31st IEEE Photovoltaic Spec. Conf.*, 2005, pp. 955–958.

- [29] K. Maydell, L. Korte, A. Laades, R. Stangl, E. Conrad, F. Lange, and M. Schmidt, "Characterization and optimization of the interface quality in amorphous/crystalline silicon heterojunction solar cells," *J. Non-Cryst. Solids*, vol. 352, no. 9–20, pp. 1958–1961, Jun. 2006.

**Sangwook Lee** received the B.Sc. and M.S. degrees in electrical and electronic engineering from Yonsei University, Seoul, Korea, in 2009 and 2011, respectively.

He is currently with Samsung Electronics, Seoul.

**Kwanghyun Lee** received the B.Sc. degree in physics in 2007 from Yonsei University, Seoul, Korea, where he is currently working toward the Ph.D. degree in the Department of Physics.

**Juree Hong** received the B.Sc. degree in electrical and electronic engineering in 2009 from Yonsei University, Seoul, Korea, where she is currently working toward the Ph.D. degree in the School of Electrical and Electronic Engineering.

**Seongil Im** received the B.Sc. and M.S. degrees in metallurgical system engineering (MSE) from Yonsei University, Seoul, Korea, in 1984 and 1986, respectively, and the Ph.D. degree from the University of California, Berkeley, in 1994.

After two years of postdoctoral experience in California Institute of Science and Technology (CALTECH), he joined Yonsei University as an Assistant Professor with the Department of MSE in 1997. In order to support the applied physics field, he moved to the Department of Physics from the

Department of MSE in 1999 and was promoted to a Full Professor in the same department in 2004. For the last five years, he has published more than 70 journal papers on organic and inorganic oxide transistor devices. His current research interests are thin-film devices and electronics adopting glass or plastic substrates.

**Ja Hoon Koo** received the B.Sc. degree in electrical and electronic engineering in 2010 from Yonsei University, Seoul, Korea, where he is currently working toward the M.S. degree in the School of Electrical and Electronic Engineering.

tronic Engineering.

Seulah Lee received the B.Sc. and M.S. degrees in electrical and electronic engineering in 2009 and 2011, respectively, from Yonsei University, Seoul, Korea, where she is currently working toward the Ph.D degree in the School of Electrical and Elec-

**Taeyoon Lee** received the B.Sc. and M.S. degrees in metallurgical system engineering from Yonsei University, Seoul, Korea, in 1995 and 1997, respectively, and the Ph.D. degree in materials science and engineering from the University of Illinois at Urbana-Champaign, Champaign, in 2004.

He joined Intel Corporation as a Senior Process Engineer in the Flash Memory Group in 2005 and worked there for almost three years, where he gained extensive research and development experience in nonvolatile memory device and integrated chip man-

ufacturing. He is currently a Professor with the School of Electrical and Electronic Engineering, Yonsei University. His research interests focus on exploring 1-D and 2-D nanobuilding blocks and novel devices including nanowires (Si, SiGe, ZnO, etc.) and carbon materials (carbon nanotube, graphene, and graphene oxide). Furthermore, he also has interest in flexible electronics fabricated by transfer printing method, bioinspired surfaces with multifunctions, and self-assembled quantum dots.